Chap3) Sequential Logic Design

[3. Sequential Logic Design]

<목차>

3.1 Introduction

3.2 Latches and Flip-Flops

- 3.2.1 SR Latch

- 3.2.2 D Latch

- 3.2.3 D FIip-Flop

- 3.2.4 Register

- 3.2.5 Enabled Flip-Flop

- 3.2.6 Resettable Flip-Flop

- 3.2.7 Transistor-Level Latch and Flip-Flop Designs

- 3.2.8 Putting It All Together

3.3 Synchronous Logic Design

- 3.3.1 Some Problematic Circuits

- 3.3.2 Synchronous Sequential Circuits

- 3.3.3 Synchronous and Asynchronous Circuits

3.4 Finite State Machines

- 3.4.1 FSM Design Example

- 3.4.2 State Encodings

- 3.4.3 Moore and Mealy Machines

- 3.4.4 Factoring State Machines

- 3.4.5 Deriving an FSM from a Schematic

- 3.4.6 FSM Review

3.5 Timing of Sequential Logic

- 3.5.1 The Dynamic Discipline

- 3.5.2 System Timing

- 3.5.3 Clock Skew

- 3.5.4 Metastability

- 3.5.5 Synchronizers

- 3.5.6 Derivation of Resolution Time

3.6 Parallelism

3.1 Introduction

Sequential Logic의 출력값은 현재 입력값과 이전 입력값에 영향을 받는다.

죽, 메모리를 갖는다. 이전 입력값은 State라 표현한다.

이 챕터에서는 래치와 플립플롭을 다룰 것이고,

이것들은 1비트 State를 담는 간단한 Sequential Circuit이다.

(1).Finite State Machine은 Sequential Circuit을 디자인하는 방법이고,

(2).Parallelism은 Sequencial Circuit의 속도를 올리는 방법이다.

3.2 Latches and Flip-Flops

When power is first applied to a sequential circuit, the initial state is unknown and usually unpredictable. It may differ each time the circuit is turned on.

1)SR Latch

Nor게이트 2개로 구성된다. Set / Reset

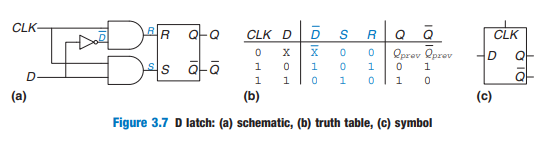

2)D Latch

SR 래치는 무엇을 넣을 것인지, 언제 넣을 것인지를 고민해야해서 불편하다. (R,S=1인 요상한 경우)

반면 D 래치는 R,S=1인 경우가 없다.

D래치는 SR래치를 이용해 업그레이드 한 것.

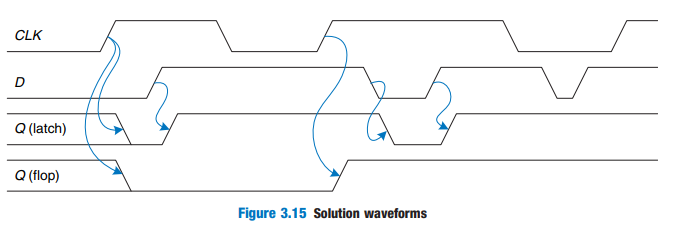

D는 넣을 데이터이다. 그리고 CLK를 보면 Edge 트리거 아니다.

| 구분 | Latch | Flip Flop |

| 기초 원리 | Level-Trigger 방식 | Edge-Trigger 방식 |

| 부품 | 논리게이트 | Clock과 Latch |

| CLK 신호 | X | O |

3)D Flip-Flop

Clock에 의해 제어 되는 2개의 D Latch로 구성된다.

CLK가 0때는 Q가 N1으로 가고 CLK 1일 때는 N1이 Q로 간다.

즉, D Flip-Flop은 CLK Rising Edge에서 D값을 Q로 옮기고 이를 기억한다.

Clock Edge는 데이터 업데이트 할 때 쓰는 것.

삼각형 기호로 잡혀있는 것은 Edge-Triggered Clock Input이다.

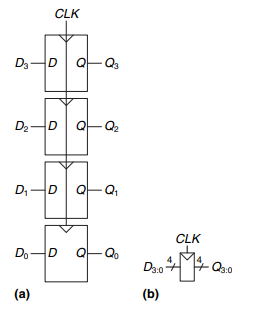

4)Register

N비트 레지스터는 N개의 플립 플롭과 공통 CLK Input으로 구성된다.

그러므로 레지스터는 동시에 업데이트 된다. 레지스터는 중요한 Building Block of Most Sequential Circuits

5)Enabled Flip-Flop

Enabled Flip-Flop은 EN입력을 추가한 것이다. EN입력은 클럭 엣지에서 데이터를 실을 지를 정하는 것이다.

EN=True 일때, Enabled Flip-Flop은 일반적인 D Flip Flop 처럼 행동한다. False인 경우 상태를 유지한다.

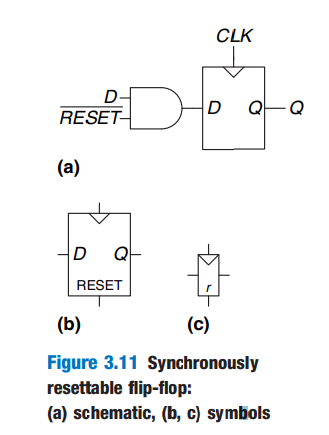

6)Resettable Flip-Flop

Resettable Flip-Flop은 Reset입력을 추가한 것이다.

Reset입력은 false 일 경우, 일반적인 D플립플롭처럼 행동한다.

True인경우에는 D 값은 무시하고 출력은 0이다.

이 플립 플롭은 Synchronously 혹은 Asynchronously 2가지 방식이 있음

(*active low : 0일 때 동작하는 녀석)

7)Transistor-Level Latch and Flip-Flop Designs

Figure 3.12 (a)는 기본적인 CMOS Latch이다

하지만, Transmission Gate 가 Off 일때 , Q는 D로부터 고립되어있어 Latch의 상태는 불명확해진다.

이 기본적인 CMOS Latch는 2가지 문제를 가진다.

-1).Floating Output node

출력이 불명확하다. Q는 어느 Gate에서도 자체의 값을 가지지 못한다.

그래서 Q는 Floating or Dynamic Node 라고 불린다.

노이즈나 누설 전하에 의해 Q가 방해를 받을 수도 있다.

-2).버퍼 없음.

버퍼가 없는 경우 상업용 칩에서는 오작동을 일으킬수 있다.

노이즈에 의해서 CLK=0인데도 nMOS/ pMOS 를 작동시킬 수 있다.

트렌지스터가 대칭적이므로 이것이 Q가 인풋 D에 영향을 주는 등의 역방향 영향으로 진행될 수 있다.

Figure 3.12(b)는 상용 칩에서 사용되는 더 바람직한 12-TR D Latch 이다.

Inverter I1, I2는 입력과 출력 값을 완화한다.

N1에서는 Latch의 값이 저장되고 Inverter I3와 Tristate Buffer T1은 N1을 Static Node로 바꾸는 피드백을 준다.

CLK=0일때, 노이즈에 의해 생기는 N1은 T1에 의해 알맞은 값을 다시 찾는다.

위 사진은 2개의 Static Latch이다.

*Tristate Buffer

8)Putting It All Together

3.3 Synchronous Logic Design

이 섹션에서는 신기한 회로들을 분석할 것이다. 이것들은 Synchronous Sequential Circuits과

Dynamic Discipline의 개념에 대해 설명한다. 이 두가지 개념을 통해서 Sequential System을

분석하고 설계하는 능력을 기를 수 있다.

1)Some Problematic Circuits

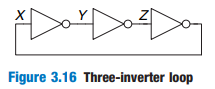

-EX1) Astable Circuits

이 회로는 불안정적인 회로이다. 각 인버터의 Propagation Delay가 1ns일때 다음과 같은 반응을 보인다.

6ns를 주기로 각 노드의 값이 진동한다. 이 회로를 Ring Oscillator라고 한다.

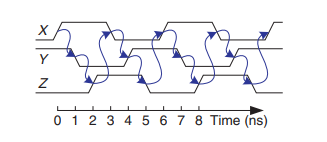

-EX2) Race Condition

아래 그림은 Ben Bitdiddle이 만든 D래치이다. 그는 더 적은 Gate를 쓴 본인의 D 래치가 기존의 것보다 좋다고

주 장하는데 이는 맞는 말이 아니다.

진리표를 보면 맞는 것 같지만 특정 게이트가 다른 게이트보다 느릴 경우 작동하지 않는

Race Condition을 가지고 있다.

이것은 출력이 입력에 바로 피드백을 주는 Asynchronous Circuit의 예이다.

Asynchronous Circuit은 로직 게이트를 지나는 2개의 길 중에서 어느 것이 더 빠른지에 따라 그 특성이

정해지는 Race Condition으로 악명이 높다.

2)Synchronous Sequential Circuits

앞서 본 2개의 예시는 모두 출력이 입력으로 바로 피드백을 주는 Cyclic Path라고 불리는 루프를

포함하고 있었다. 이 2개의 예시는 Sequential Circuit이다.

Combinational Logic 은 Cyclic Path와 Race가 없다.

Combinational 회로에 입력값을 넣으면 항상 정해진 값이 Propagation Delay이내에서

나와야한다. 하지만, Cyclic Path를 가진 Sequential 회로에서는 Race와 불안정적인 특성을 갖는다.

이런 회로를 분석하는 것은 시간이 소모되는 작업이고 이 과정에서 똑똑한 사람들도 실수를 한다.

이와 같은 문제를 피하기 위해서 회로 설계자는 레지스터를 Path 내부에 넣어서 Cyclic Path을 부순다.

레지스터는 CLK에 의해 변하는 녀석이므로 우리는 회로의 상태가 CLK에 대해 Synchronized라고 할 수 있다.

Clock이 충분히 느리다면 다음 Clock Edge 전에 입력값이 모든 레지스터에 정착할 수 있으며,

모든 Race가 없앨 수 있다.

따라서, 피드백 Path에서 레지스터를 사용하는 것은 Synchronous Sequential Circuit을 정의하는 데 도움이된다.

회로라는 것은 Input/Output Terminal과 Functional/Timing Specification 에 의해 정의된다.

Sequential Circuit은 유한하고 개별적인 State를 갖는다.

Rising Edge를 통해 State 변화가 발생하는 시간을 알 수 있다.

Functional Specification을 통해 다음 State와 현재 State 그리고 입력값과 현재 State의 가능한 조합에 대한 출력 값을 구체화할 수 있다.

Timing Specification은 Rising Edge부터 Output 값이 변하기 전까지의 시간에서

Tpcq (Upper Bound)와 Tccq (Lower Bound) 로 구성된다.

또한, Rising Edge 기준으로 입력값이 언제 안정되는지를 나타내는

T setup, T hold로도 구성된다.

*Synchronous Sequential Circuit 구성의 규칙

▶ Every circuit element is either a register or a combinational circuit

▶ At least one circuit element is a register

▶ All registers receive the same clock signal

▶ Every cyclic path contains at least one register.

Flip-Flop은 가장 간단한 Synchronous Sequential Circuit이다.

2가지 대표적인 Synchronous Sequential Circuit은 Finite State Machines 과 Pipeline이다.

추후에 다룰 것이다.

3)Synchronous and Asynchronous Circuits

이론적인 Asynchronous design은 Synchronous Design 보다 더

보편적이다. 왜냐하면 Clocked Registers에 제한되지 않는 시스템의 Timing 때문이다.

또, Asynchronous Circuit은 어느 피드백도 사용할 수 있기 때문이다.

하지만 Synchronous Circuit은 Asynchronous 보다 설계하기 쉽고 사용하기도 쉬운

것이 증명되었기에 모든 디지털 시스템은 Synchronous를 보통 쓴다.

물론 Asynchronous Circuit는 경우 따라 필요하기도 하다.

예를 들어 서로 다른 클럭을 갖는 시스템 간의 통신을 한다거나,

임의의 시간에 입력값을 받는등의 경우가 있다.

3.4 Finite State Machines

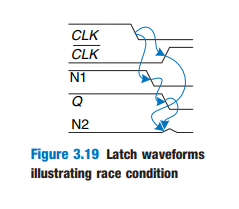

FSM은 2개의 Combinationl Logic Block, Next State Logic, Output Logic, 레지스터로 구성된다.

Next State는 Current State와 Input을 가지고 연산된 값이다.

FSM은 2가지 종류가 있다.

(1). Moore machines

The outputs depend only on the current state of the machine.

(2). Mealy machines

The outputs depend on both the current state and the current inputs.

FSM은 Synchronous Sequential Circuit을 설계하기 위한 시스템적 방식이다.

1)FSM Design Example

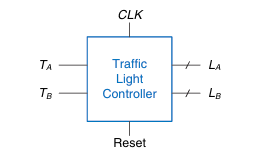

사거리에 차량을 감지하는 센서 Ta/Tb, 신호등 La/Lb , 5초 주기의 Clock, Reset Button을 이용해서

신호시스템을 구성한다고 생각해보자.

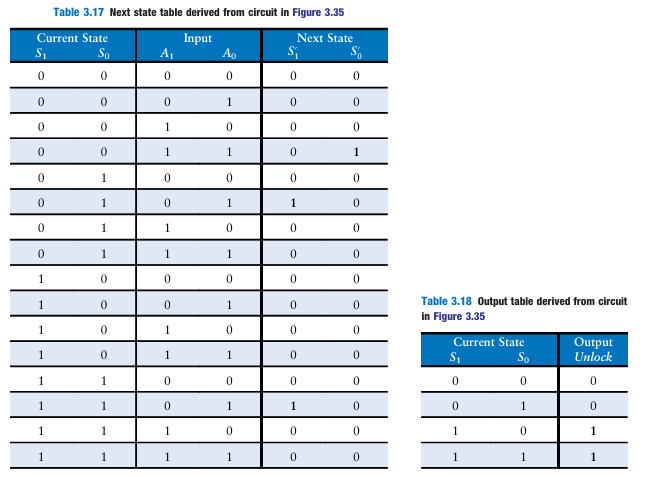

State Transition Diagram에서 원은 State를 표시하고 호는 State간의 Transition을 나타낸다.

Transition은 CLK의 Rising Edge에서 발생하므로 Diagram에서 CLK를 보려할 필요는 없다.

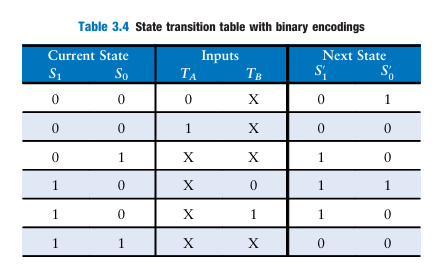

위 Diagram은 다소 추상적이다. 실제 회로를 구성하기 위해서는 State와 Output은

Binary Encoding이 필요하다.

X는 Don't Care이다. 해당 인자의 값이 현재 State에 영향을 주지 않는다는 것이다.

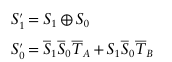

위 식은 카르노 맵으로 간략화된 식이다. (SOP로 해도 상관은 없다. 다만, 간략화하기 불편할 뿐)

Current State와 Input이 입력한 값인 것고, Next State가 결과이다. 이를 생각해서 카르노맵

그리면 된다.

*** (다음 상태) = f (입력, 현재상태 : Ta, Tb, S1, S0 )

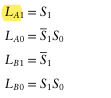

*** (출력) = f (현재 상태: S1, S0)

>> 출력은 입력을 고려해서 만들어지는 것이 아니므로 무어 머신이다.

위 출력식과 다음 상태식을 논리회로만으로 구성할 수 있다.

다만, 이런 경우 Race Condition 발생한다.(타이밍에 따라 결과값이 바뀜. >> 불안정)

그런 이유로 중간에 레지스터 넣어서 "Cyclic Path" 부순다.

2)State Encodings : One-Hot encoding

One important decision in state encoding is the choice between binary encoding and one-hot encoding.

In one-hot encoding, a separate bit of state is used for each state.

It is called one-hot because only one bit is “hot” or TRUE at any time.

For example, a one-hot encoded FSM with three states would have state encodings of 001, 010, and 100.

각 비트는 레지스트 하나씩 가지므로 Binary Encoding 보다 레지스터 개수가 더 들어간다.

0과 한개의 1의 값으로 구별하는 인코딩 방법 : 3개의 신호 구분시 001/010/100

S0에서 S1 그리고 S2 의 순환이 있다. CLK Rising Edge 마다 State가 넘어간다. 처음에 Y는 0이니

Reset 하면 S0 레지스터는 1을 담고 S1, S2는 0을 담는다. Y=1 출력. S1=1이고 Y=0.

그 다음 S2=1이고 Y=0, 그 다음 S0=1이고 Y=1

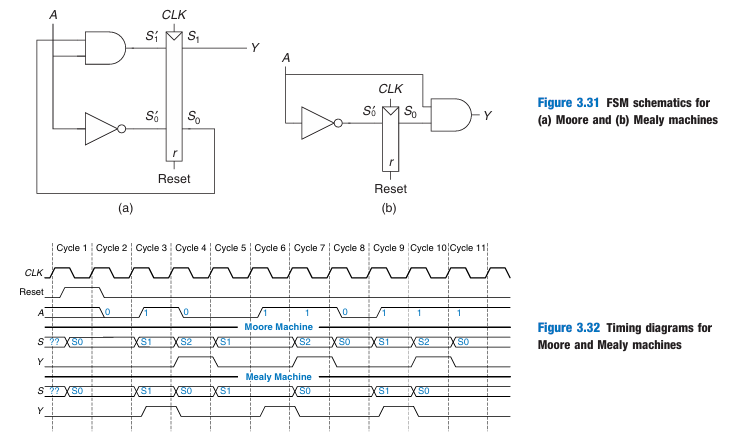

3)Moore and Mealy Machines

지금까지 출력이 시스템의 State에 따라 나오는 무어 머신의 예를 보았다.

무어머신은 State Transition 다이아그램에서 출력은 원 안에 있고, 출력이 현재 State만 고려하여 나온다.

반면, 밀리 머신은 출력이 현재 State와 입력에 따라 출력이 나오고,

출력은 호에 있다.

무어 머신이나 밀리 머신이나 각 State는 의미를 가지고 있다. 고려할 요소에 따라 다를 뿐이다.

**무어/밀리 에서 얻고자 하는 식은 "다음 상태"와 "출력"이다.

*무어 : (다음 상태) = f (입력, 현재상태)

(출력) = f (현재 상태)

*밀리 : (다음 상태) = f (입력 )

(출력) = f (입력, 현재상태)

입력은 읽을 값인 것이고 출력은 Smile이다.

3.30(a)의 경우, 무어머신이므로 단순히 현재 State에 의해서 다음 State가 정해진다. S0이면 입력과 상관없이

State는 S1이 된다. S0는 아무 값도 읽지 않은 상태이다. S1는 0을 읽고 난 상태, S2는 01을 읽고 난 상태이다.

호 위의 값은 입력값이고 원안의 값은 출력값이다. 호가 다음 State로 간다고 해서 다음 State가 입력을

고려한다는 것은 아니다.

3.30(b)에서 호 위의 값은 입력/출력이다.

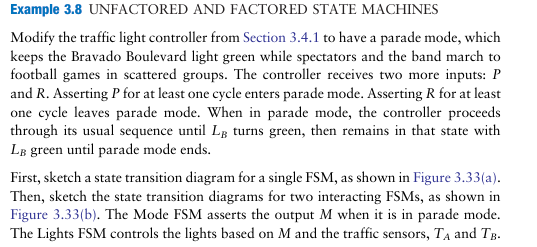

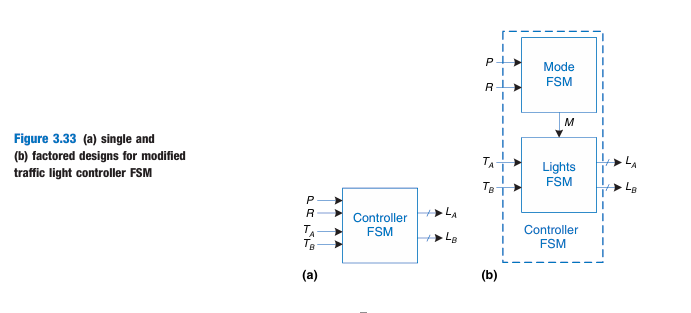

4)Factoring State Machines

복잡한 FSM은 서로 연결된 단순한 State Machines으로 구성할 수 있다.

하나의 State Machine의 결과값이 다른 State Machine의 입력값으로 작용한다.

이런 계층적이고 모듈적인 것을 Factoring of State Machines이라한다.

위에서 다루었던 신호등 문제에서 퍼레이드 모드를 추가한다.

관중과 밴드가 행진하는 동안 Barado Boulevard 거리의 빛이 녹색을 유지하는 기능이다.

이때, 입력값 2개가 추가된다 : P( 퍼레이드 모드 시작 ), R(퍼레이드 모드 정지 ). 퍼레이드 모드에서는 Lb가 녹색이

되기전 까지 이전과 같은 동작을 한다. Lb는 퍼레이드 모드 끝나기 전까지 녹색을 유지한다.

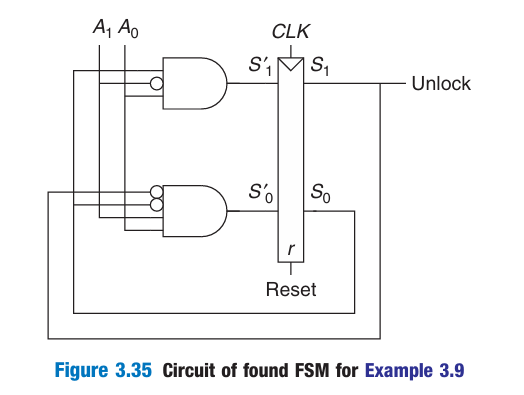

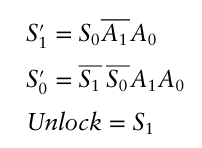

5)Deviding an FSM from a Schematic

▶ Examine circuit, stating inputs, outputs, and state bits.

▶ Write next state and output equations.

▶ Create next state and output tables.

▶ Reduce the next state table to eliminate unreachable states.

▶ Assign each valid state bit combination a name.

▶ Rewrite next state and output tables with state names.

▶ Draw state transition diagram.

▶ State in words what the FSM does.

Solution)

6)FSM Review (X)

3.5 Timing Of Sequential Logic

1)The Dynamic Discipline

2)System Timing

3)Clock Skew

4)Metastability

5)Synchronizers

6)Derivation of Resolution Time

3.6 Parallelism