DDCA 책 내용을 복습에 용이하도록 정리한 글이다.

<Chap1 에서 다루는 내용>

1. >> 컴퓨터에서 어떻게 수를 표현하는가 (Sign/Magnitude, 보수)

2. >> 컴퓨터에서 어떻게 연산을 하는가 (Logic Gate)

3. >> 회로 단계에서 이해하는 논리 회로

4. >> 컴퓨터를 구성하는 트랜지스터를 깊이 알기

[1. From Zero to One]

1.1 The Game Plan

마이크로프로세서 설계가 목적인 책이다.

1.2 The Art of Managing complexity

1)Abstraction

The critical technique for managing complexity is abstraction.

This book focuses on the levels of abstraction from digital circuits through computer architechture

2)Discipline (표준화 느낌)

Discipline is the act of intentionally restricting your design choices so that you can work more

productively at a higher level of abstraction

3)The Three -Y's : 디지털의 복잡성을 관리하기 위하여 사용

Hierarchy / Modularity / Regularity

1.3 The Digital Abstraction

1.4 Number System

1)Decimal Numbers

2)Binary Numbers

3)Hexadecimal

4)Bytes, Nibbles and All that Jazz

LSB(Least Significant Bit) 뒷자리

MSB(Most Significant Bit) 맨앞자리

5)Binary Addition

6)Signed Binary Numbers

이 단원에서 설명하고자 하는 바는 결국....

어떻게 컴퓨터는 음수를 표현하는가? 이다.

음수를 표현하는 기본적인 방법은 (1)Sign Magnitude(부호 절대값)방법이 있다.

(1)Sign-Magnitude 방법

최상위 비트 MSB 이용. MSB=1이면 그냥 부호만 - 이다.

ex) 1001(2진수) 은 -1(10진수)이다.

장점: 이 방법은 사람이 직관적으로 사용하기에 용이하다.

단점: 양수와 양수의 덧셈이나 음수와 음수의 덧셈은 어렵지 않지만,

음수와 양수의 덧셈은 절대값을 고려해야하기 때문에 회로를 만들기 번거롭다.

또한, +0, -0이 존재한다.

앞서 말했듯이 이러한 수 체계는 "컴퓨터 세상"에서 편의하게 연산을 하기 위함이다.

그런데, 컴퓨터는 가산기만을 이용하여 연산을 하기 때문에, 뺄셈을 덧셈을 변환하여 계산한다.

A-B= A+(-B) .이러한 관점에서 보수라는 개념이 등장한다.

보수란?

보수는 보충해주는 수. 즉, 어떤 수를 만들기 위해 필요한 수이다.

ex) 4(10진수)의 10의 보수는 6이다.

ex) 2(10진수)의 10의 보수는 8이다.

보수란 개념을 이용하면 음수를 만드는 다른 방법을 이용할 수 있다. (2) 1의보수. (3) 2의 보수이다.

2가지 방식 모두 Sign-Magnitude와 달리, n비트의 MSB 는 -2^(n-1)을 나타낸다.

(2). 1의 보수

어떤 수 n과의 합이 1이 되는 수이다. ex) 0011의 보수는 1100이다.

왜 이렇게 정의하는지 잘 이해는 안가는데 <합해서 각 자리가 1이 되는 수> 라고 이해하면 좋다.

1의 보수는 양수를 써두고 각 비트를 반전 시켜서 음의 값을 표현한다.

ex) 01(2)은 +1, 00(2)은 +0, 11(2)은 -0, 10(2)은 -1이다.

여기서 보이듯이 +0과 -0이 구분되기 때문에 이것이 단점이다.

(3). 2의 보수

1의 보수를 보완한 방식이다. <01(2)은 +1, 00(2)은 +0, 11(2)은 -0, 10(2)은 -1>인 1의 보수를 보자.

-0이 1의 보수의 문제이므로 -0을 정의 하지 않으려면 양수의 값을 반전하고 +1을 더하면 된다.

그러면 -0은 100(2)이 되어 정의가 불가능해진다.(물리적으로 2비트로 고정되어있다는 가정이기 때문)

위의 설명은 1의 보수를 보완하는 입장의 이해이다.

이런 이해와 달리 그냥 어떻게 쓰는지 이해하는 방식도 있다.

1의 보수에서 합해서 각 자리가 1이 되는 수라고 정의 했으니

2의 보수는 1의 보수에 +1만 하면 되는 것이다.

보수가 결국 어떤 수를 만드는 데 필요한 수라고 했으니,

1을 만드는데 보충하는 수를 구하고 +1을 더하면 결국, 2를 만드는 수가 된다. 즉, "2의 보수"

(1을 만드는데 보충하는 수 = 1의 보수. 1의 보수는 <합해서 각 자리가 1이 되는 수>)

ex) 0101(2) 는 +5(10), 1011(2)는 -5(10)

*Range of N-bit numbers

| System | Range |

| Unsigned | [0, 2^n-1] |

| Sign/Magnitude | [-2^(n-1)+1, 2^(n-1)-1] |

| Two's Complement | [-2^(n-1), 2^(n-1)-1] |

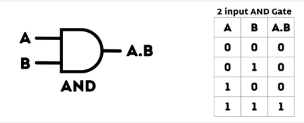

1.5 Logic Gates ************추가적으로 정리 필요

1)Not Gate

2)Buffer

3)And

4)Or

5)XOR

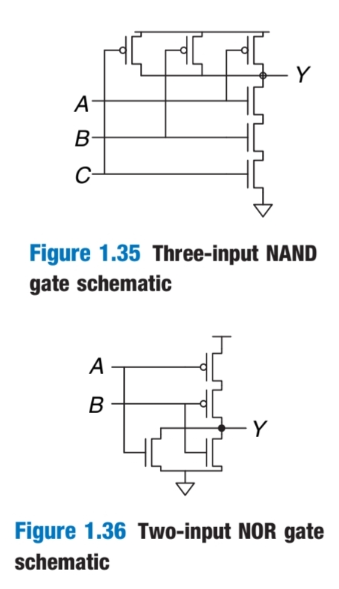

6)NAND

7)NOR

8)XNOR

1.6 Beneath The Digital Abstraction

1)Supply Voltage

0v: GND, 5v:Vdd

Vdd는 시간이 흐를 수록 값이 내려가는 쪽으로 발전했다. Power를 아끼고 트랜지스터의 Overloading을 피하려고

점점 Vdd값이 내려간다.

2)Logic Level

The mapping of a continuous variable onto a discrete binary variable is done y defining "Logic Level"

0과 1이라고 인정할 수 있는 전압의 기준 값 = Logic Level

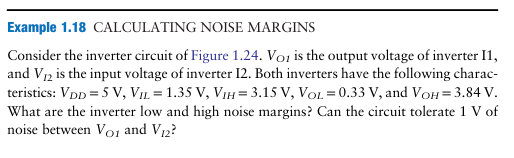

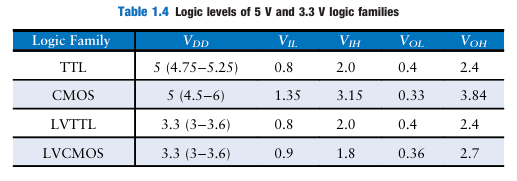

Voh,Vol,Vih,Vil : Output / Input 의 High/Low Logic Level이라 부른다.

Forbidden Zone에 해당하는 Logic Level은 Gate의 반응을 예측할 수 없는 레벨

Voh> Vlh, Vil>Vol 이어야만 Driver, Receiver 작동

Noise Margin : NMh, NMl (노이즈 타도 되는 허용 범위, 여분의 범위)

3)Noise Margin

Vo1과 Vi2 사이에 노이즈를 1V정도 먹는다고 보면 Vo1이 최소한으로 나올 수 있는 출력은 3,84V 즉, 노이즈 타면

2.84V까지 떨어지므로 회로가 정상 작동하지 않을 수 있다.

4)DC Transfer Charcteristics

DC는 Vdd과 0으로 구성되지만 실제로는 Vdd과 0으로 변하는 사이에 점진적으로 변화한다.

전압이라는 것은 실제로는 변하는 값이므로 dV(Y)/dV(A)=-1 지점을 Logic Level로 잡아서 사용한다

V(A) : 입력전압

V(Y) : 출력 전압

5)The Static Discipline

입력값이 Forbidden Zone에 빠지지 않도록 하기 위해 Logic Gate는

"Static Discipline"을 따른다.

Static Discipline은 회로의 모든 요소가 논리적으로 타당한 출력을 할 것을 요구한다.

자유로운 아날로그 대신 다소 자유롭지 못한 디지털을 사용하면서 생산성을 올린다.

+추가>>

1970-1990 사이를 장악한 Logic Families는 4가지 있다.

(1). Transistor - Transistor Logic (TTL)

(2). Complementary Metal - Oxide - Semiconductor Logic (CMOS)

(3). Low Voltage CMOS Logic ( LVCMOS)

(4). Low Voltage TTL Logic (LVTTL)

1.7 CMOS Transistors (필수적인 이야기는 아님)

*초기 컴퓨터는 릴레이와 진공관을 사용했다.

*하지만, 현대 컴퓨터는 Transistor를 사용한다. 왜냐하면 더 작고 저렴하고 안정하기 때문이다.

*대표적인 TR은 2가지 있다.

* -(1) Bipolar Junction Transistor (BJT)

* -(2) Metal - Oxide - Semiconductor Field Effect Transistor(MOSFET, MOS트랜지스터)

1)Semiconductors

*MOS TR은 실리콘으로 구성된다.

*실리콘은 4개의 전자를 가지고 있고 이는 인접한 원자와 4개의 결합을 만들 수 있다.

*이를 통해 Crystalline Lattice를 만든다.

*Lattice는 실질적으로 Cubic Crystal을 만든다.

*실리콘 자체로는 좋지 않는 전도체이다.

*전자 4개가 전부 다른 Si 전자와 공유결합(Covalent Bond)하기 때문이다. (Figure 1.26(a))

*이러한 이유로 소량의 불순물을 섞어쓴다.

* AS를 섞으면 전자 1개가 남는다. (n-Type)

* B를 섞으면 정공 1개가 생긴다. (p-Type)

2)Diodes

*p-Type 실리콘과 n-Type 실리콘의 결합을 Diode라 한다. 물리적 결합이다.

* p-Type Region = Anode

* n-Type Region = Cathode

*Anode의 전압이 Cathode 보다 높으면 A에서 C로 전류흐르고, 이를 Forward Biased라 표현한다.

*반대로 Cathode 접압이 더 높으면 전류는 흐르지 않고, 이를 Reverse Biased라 표현한다.

3)Capacitors(생략)

4)nMOS and pMOS Transistors

*MOSFET은 여러 겹의 전도체(Conducting Material)와 절연체(Insulting Material)의 집합이다.

*MOSFET은 실리콘으로 만들어진 얇은 Wafer로 만들어진다.

*제조 과정은 다음과 같다

* >>아무것 공정도 거치지 않은 Bare Wafer로 시작

* >>Si 도핑 과정 거침(이 과정에서 사용자가 원할 때 작동하도록 Wafer가 패턴화됨)

* >>Chip 또는 Dice라 불리는 사각형 모양으로 자른다.

* >>Chip의 성능을 검사한다.

* >>회로와 연결할 수 있는 금속 핀들이 박힌 플라스틱 혹은 세라믹 패키지에 넣는다.

*MOSFET은 Gate(Conducting Layer) - SiO2(절연체) - 실리콘 웨이퍼(Substrate : 기판) 순으로 구성

*Gate가 Metal이라서 MOSFET의 M은 Metal이다.

*현대에는 Gate에 Polycrystalline Silicon 쓴다. ( 높은 온도에서 녹지 않기 때문)

*MOSFET은 Voltage - Controlled Switch 역할을 한다.

*Gate - Voltage가 Electric Field 만들고, 이 Field(전기장)는 Source와 Drain 사이에서

*On 또는 Off 되도록한다. 이 특성에서 "Field Effect Transistor" 라는 말이 나온것이다.

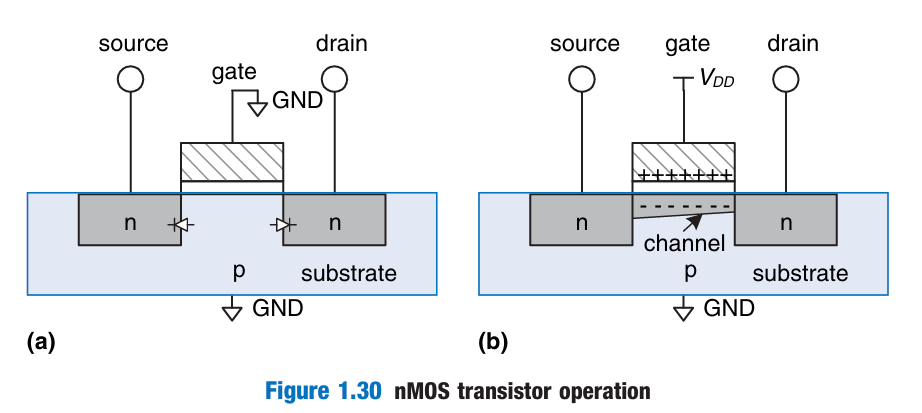

*n MOS에 대해 자세히 살펴보자

*n MOS는 Substrate가 GND에 연결되어있다.(Figure 1.30(a))

*Figure 1.30(a)를 보면 Gate=0V=GND

*Source와 Drain 사이의 2개의 Diode는 "Reverse Biased" 상태이다.

*따라서, Source나 Gain으로 전류가 흐르는 길이 없다.

*이는 곧, TR Off이다.

*Figure 1.30(b)를 보면 Gate = Vdd이고

*Conducting Layer와 Substrate 사이 Insulting Layer 상하부에 정공(양공)과 전하가 생긴다.(캐패시터 느낌)

*Voltage가 충분히 크다면 Gate 아래 영역에 많은 음전하가 모여서 Gate 아래 영역이 p -Type영역에서

*n-Type 영역으로 바뀌게 된다.

*이 바뀐 영역을 Channel이라 부른다.

*따라서, TR은 n-Type Source에서 Channel을 거쳐 n-Type Drain으로 통하는 길이 생긴 것이다.

*전하가 Source에서 Drain으로 흐르고 TR은 On이 된다.

*TR을 켤 수 있는 Gate Voltage를 Threshold Voltage(Vt)라고 한다.

*통상적으로 0.3V~0.7V이다.

*p-MOS는 n-MOS와 반대로 작용한다.

*아쉽게도 MOSFET은 완벽한 스위치가 아니다.

*nMOS는 0은 잘 통과시키고, 1은 잘 통과시키지 못한다.

*자세히 말하자면 Drain은 오직 0과 Vdd-Vt 사이에서만 값이 흔들린다.(??? 이해안됨)

*pMOS는 1은 잘 통과시키고, 0은 잘 통과시키지 못한다.

*n MOS는 p Substrate / p MOS는 n Substrate가 필요하다.

*동일한 Chip에서 이 2가지를 사용하기 위해 제조 공정에서는 p-Type Wafer로 제조를 시작한다.

*그리고 pMOS TR이 가야만 하는 Wells이라는 n-Type Region을 심는다.

*이 2가지 Type을 만들어내는 제조 공정을 CMOS라고 부른다. (Complemetary MOS: 보완한 MOS?)

*현재 대다수를 차지하는 방식이다.

*요약하면 CMOS 공정은 2가지 종류의 전기 제어 스위치를 제공한다.

*Gate는 Source와 Drain 사이 전류를 통제하고

* n-MOS에서 Gate=0 >>Tr ON / Gate=1 >>Tr OFF

5)CMOS NOT Gate

6)Other CMOS Logic Gates

nMOS는 0을 잘 통과시키고, pMOS는 1을 잘 통과시킨다.

따라서, nMOS는 GND와 출력 사이에서 풀다운 역할을 하고

pMOS는 Vcc와 출력 사이에서 풀업 역할을 한다.

*Conduction Complement Rule

nMOS TR이 직렬(병렬) 연결되어 있다면 pMOS TR은 병렬(직렬)로 연결되어야한다.

7)Transmission Gate

*회로 설계자들은 0과 1이 잘 통과하는 이상적인 스위치를 설계함.

*Transmission Gate 혹은 Pass Gate라고 불린다.

*제어 신호는 오직 Enable 뿐이다.

8)Pseudo - n MOS Logic

*Pseudo([쑤도] : 유사의, 거짓의, 가짜의 >> 접두사로 Pseud로 쓰이기도함)

*

* TR의 직렬 연결은 병렬 연결보다 저항을 많이 먹고 더 느리다.

* 또한, pMOS TR 이 nMOS TR보다 더 느리다.

* 정공이 실리콘 Lattice 주변을 전자보다 더 빨리 움직일 수 없기 때문이다.

* Pseudo nMOS Logic은 느린 pMOS 조합을 항상 켜져있는 하나의 약한 pMOS TR로 대체한다.

* 이러한 pMOS TR을 "Weak Pull Up" 이라 한다.

* nMOS가 전부 OFF일때 풀업되고 nMOS중 하나라도 ON 되면 Y=0이다.

* 이러한 Pseudo nMOS Logic은 많은 입력값을 갖는 더 빠른 NOR게이트를 만드는데 이점이 있다.

* 또한 특정 메모리와 논리 배열에 유용하다.

* 단점은 출력이 0일때, Vdd와 GND 사이에 Short Circuit이 존재한다.

* pMos와 nMOS 둘 다 ON인 경우 Short Circuit이 지속적인 전력을 끌어당기기 때문에

* Pseudo-nMOS는 드물게 사용해야한다.

1.8 Power Consumption

* Dynamic Power : Capacitance 를 0과 1의 신호 변화로 충전할 때 P=1/2C(Vdd^2)f

* Static Power : 신호가 바뀌지 않고 시스템이 이상적일 때 P=IddVdd

* Power Consumption = 사용된 에너지 / 시간

* Logic Gate와 전선은 Capacitance를 갖는다.(nMOS/pMOS의 Channel 떠올려라)

* * 공식 1: 전력(Power) P=VI

* * 공식 2:전류 I=Q/t

* * 공식 3: 커패시턴스 C=Q/V

* P static은 정적인 상태에서 구하므로 공식1과 다르지 않다.

* p dynamic은 다르게 봐야한다. Vdd는 일정하지만 Idd는 일정하지 않다.

* Idd를 새롭게 표현하는 데 있어서 캐패시턴스와 진동수(또는 주기)를 이용할 수 있다

* I=Q/t이고 C를 알고 있으므로 I=Q/t=CVdd/t 라고 표현할 수 있다.

* 이때, t는 충전과 방전의 주기로 둔다면 I=CfVdd이다.

* P=CfVdd * Vdd

* 다만 충전한 만큼 방전하기 때문에 2로 나누어 쓴다.

* 절대로 충전과 방전시간이 같기 때문에 2로 나눈 것이 아니고 2가 주기를 나누지도 않는다.

'4_전공 과목 > 디지털공학' 카테고리의 다른 글

| Chap 2+) 가산기 (0) | 2024.03.03 |

|---|---|

| Chap3) Sequential Logic Design (0) | 2024.02.06 |

| Chap 2) Combinational Logic Design (0) | 2024.01.18 |